| Product Description |

| CPU | •Octa core ARM Cortex-A55, up to 2GHz |

| •32 KB L1 I-cache and 32 KB L1 D-cache per A55 core |

| •Single-core RISC-V, up to 200MHz |

| GPU | •ARM G57 MC1 GPU |

| •Supports OpenGL ES 3.2/2.0/1.1, Vulkan 1.1/1.2/1.3, OpenCL 2.2 |

| •Anti-aliasing algorithm |

| •High memory bandwith and low power cunsumption in 3D graphics processing |

| ROM | •Support 8bit data bus, Support 8GB/16GB/32GB, max 128GB |

| •eMMC V5.1 |

| •Support boot from eMMC |

| RAM | •Support one LPDDR4 and LPDDR4x |

| •Support 32-bit databus, default 2GB, max 4GB |

| •Clock frequency up to 1200MHz for LPDDR4x |

| Video Decoding | •Supports ITU-T H.265 Main/Main 10, level 6.1 |

| •Maximum video resolution:8192x4320, decoding rate:3840x2160 60fps |

| •Supports VP9 Profile0/Profile2, level 6.1 |

| •Maximum video resolution:8192x4320, decoding rate:3840x2160 60fps |

| •Supports ITU-T H.264 Base/Main/High Profile level 4.2 |

| •Maximum video resolution:3840x2160, maximum decoding rate: 3840x2160 30fps |

| Video Encoding | •H.264 BP/MP/HP encoding, supports 4K 25fps 8bits |

| •Maximum resolution:4096x4096 (16 megapixels) |

| •Supports I/P frame type, supports CBR, VBR and FIXEDQP modes |

| •Supports JPEG baseline encoding, JPEG encoder supports 4K 15fps |

| •JPEG encoder support YUV420, YUV422 and YUV 444 format |

| •MJPEG baseline encoding up to 4K 15fps |

| Vedio Input | •Supports one individual ISP, with maximum resolution of 3264x4224 |

| •Maximum frame rate of 8M 30fps 2F-WDR |

| Supports WDR spilt, 2D/3D noise reduction, bayer interpolation, sharpen, white balance and color enchancement |

| •8M 30fps ARW12 2F-WDR, size up to 3264(H)x2448(V) |

| •2+2-lane MIPI interface |

| •Parallel CSI, supports 8-bit width width |

| Audio | •Two audio DAC channels, 16 bit and 20 bit sample resolution |

| •Supports one stero headphone out HPOUTL/R |

| •One microphone inputs MICIN1P/1N |

| •Four I2S/PCM external interfaces (I2S0, I2S1, I2S2, I2S3) for connecting external power amplifer and MIC ADC |

| •Compliant with standard Philips Inter-IC sournd (I2S) bus specification |

| •Supports multiple function clocks, supports TX/RX DMA slave interface |

| Display | •Supports RGB interface with DE/SYNC mode, up to 1920x1080 60fps |

| •Supports serial RGB/dummy RGB interface, up to 800x480 60fps |

| •Supports dual LVDS, up to 1920x1080 60fps, single LVDS 1366x768 60fps |

| •Supports 4-lane MIPI DSI, up to 1280x720 60fps, 1920x1200 60fps |

| •Supports 4+4-lane MIPI DSI, up to 2560x1600 60fps |

| •Supports eDP1.3, up to 2.5K 60fps, 1-lane, 2-lane or 4-lane, up to 2.7Gbit/s per lane |

| •Video formats:RGB, YCbCr4:4:4, and YCbCr4:2:2 |

| •One TCON TV controller (TCON_TV1) for eDP 1.3 |

| •Up to 2.5K 60fps, 8bit or 10bit pixel depth |

| Touch Panel | •Supports I2C or USB capacitive touch panel |

| •Supports I2C resistive touch panel by external IC |

| SD/MMC | •Support SD V3.0, SDIO 3.0 |

| •Support MMC 4.51 |

| •Support 1-bit or 4-bit data bus |

| PCIe | •Supports one PCIe 2.1 |

| •Supports Gen1(2.5 Gbit/s), Gen2 (5.0 Gbit/s) speed |

| •Support 62.5MHz/125MHz operation on PIPE interface for Gen2/GEN2 |

| USB | •Total 3xUSB,two USB 2.0+one USB3.0; or 3xUSB2.0 |

| •One USB2.0(USB0), HS 480 Mbit/s, FS 12Mbit/s, LS 1.5Mbit/s |

| •One USB 2.0 host, , HS 480 Mbit/s, FS 12Mbit/s, LS 1.5Mbit/s |

| •One USB3.1, compliant with USB3.1 GEN1 specification(Reuse on the PICe) |

| •USB 2.0 UTMI+PHY(USB2), USB3.1 PIPE PHY(USB3) |

| •Super-speed 5Gbit/s for USB3.1 PHY, HS FS LS for USB2.0 |

| SPI | •Up to 3 SPI controllers |

| •Supports multiple SPI modes |

| •Supports STR mode and DTR mode, and DTR mode supports DQS signal |

| •High speed clock frequency, 150MHz for STR mode, 100MHz for DTR mode |

| •Programmable delay between transactions |

| •Supports control signal configuration |

| TWI | •Up to 9 TWI controllers, compliant with I2C bus standard |

| •7-bit and 10-bit device addressing modes |

| •Standard mode (up to 100Kbit/s) and fast mode (up to 400 Kbit/s) |

| •Supports general call and start byte |

| •Slave mode supports interrupt on address detection |

| UART | •Up to 8 uart controllers, compatible with industry-standard 16450/16550 UARTs |

| •Uart0 used for debug, Each of them is 128 bytes for UART1, UART2, UART3, UART4, UART5, UART6, and UART7 |

| •Embedded two 64-byte FIFO for TX and RX operation respectively |

| •Supports TX/RX DMA salve controller interface |

| EMAC | •One GMAC interface for connection external Ethernet PHY |

| •10/100/1000 Mbit/s Ethernet port with RGMII and RMII interfaces |

| •Supports both full-duplex and half-duplex operations |

| •Compliant with IEEE 802.3-2002 standard |

| •Supports a variety of flexible address filtering modes |

| LRADC | •1 channel LRADC input, 6-bit resolution |

| •Supports hold key and general key |

| •Supports normal, continue and single work mode |

| PWM | •16 independent PWM channels for PWM controller |

| •Supports PWM continuous mode output |

| •Supports PWM pluse mode output and the pulse number is configurable |

| Security | •Supports AES symmetrical algorithm |

| •Key size: 128/192/256 bits, CFB mode includes: CFB1, CFB8, CFB64, CFB128 |

| •CTR mode includes:CTR16,CTR32, CTR 64 and CTR128 |

| •Supports ECB, CBC, CTS, OFB, CBC-MAC and GCM modes |

| •Supports DES symmetrical algorithm,CTR mode, includes: CTR16, CTR32, CTR64 |

| •Supports ECB, CBC and CBC-MAC mode |

| •Supports 3DES, Hash algorithms, Randon bit generator algorithms |

| Others | •External connect a 32.768 kHz low-frequency oscillator for count clock |

| •Supports Two THS controllers, averaging filter sensor reading |

| •Watchdog timer, supports 12 initial values |

| •Two CIR_RX interfaces, full physical layer implementation, support NEC format infra data |

| Configurable LED output high/low level width, configurable LED reset time |

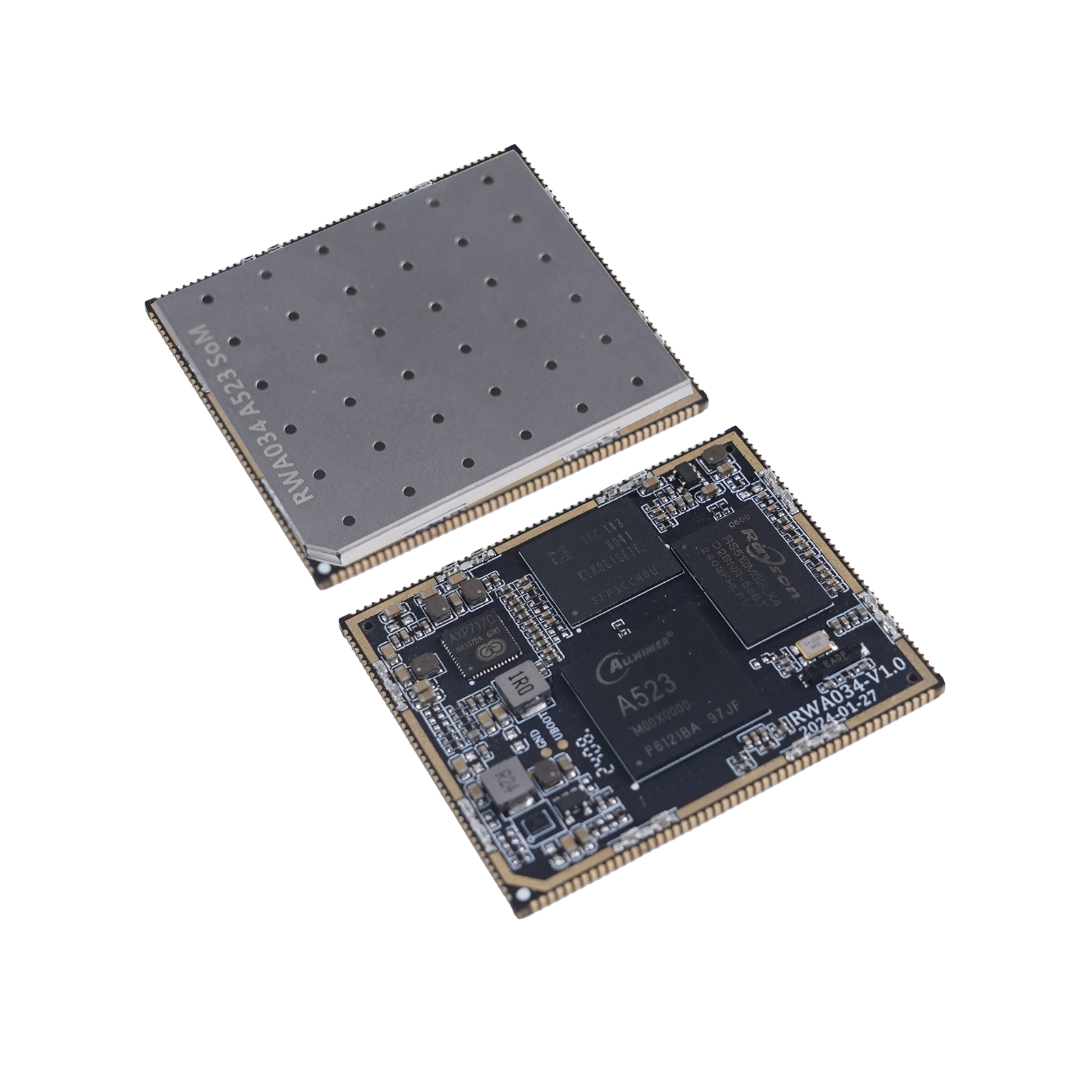

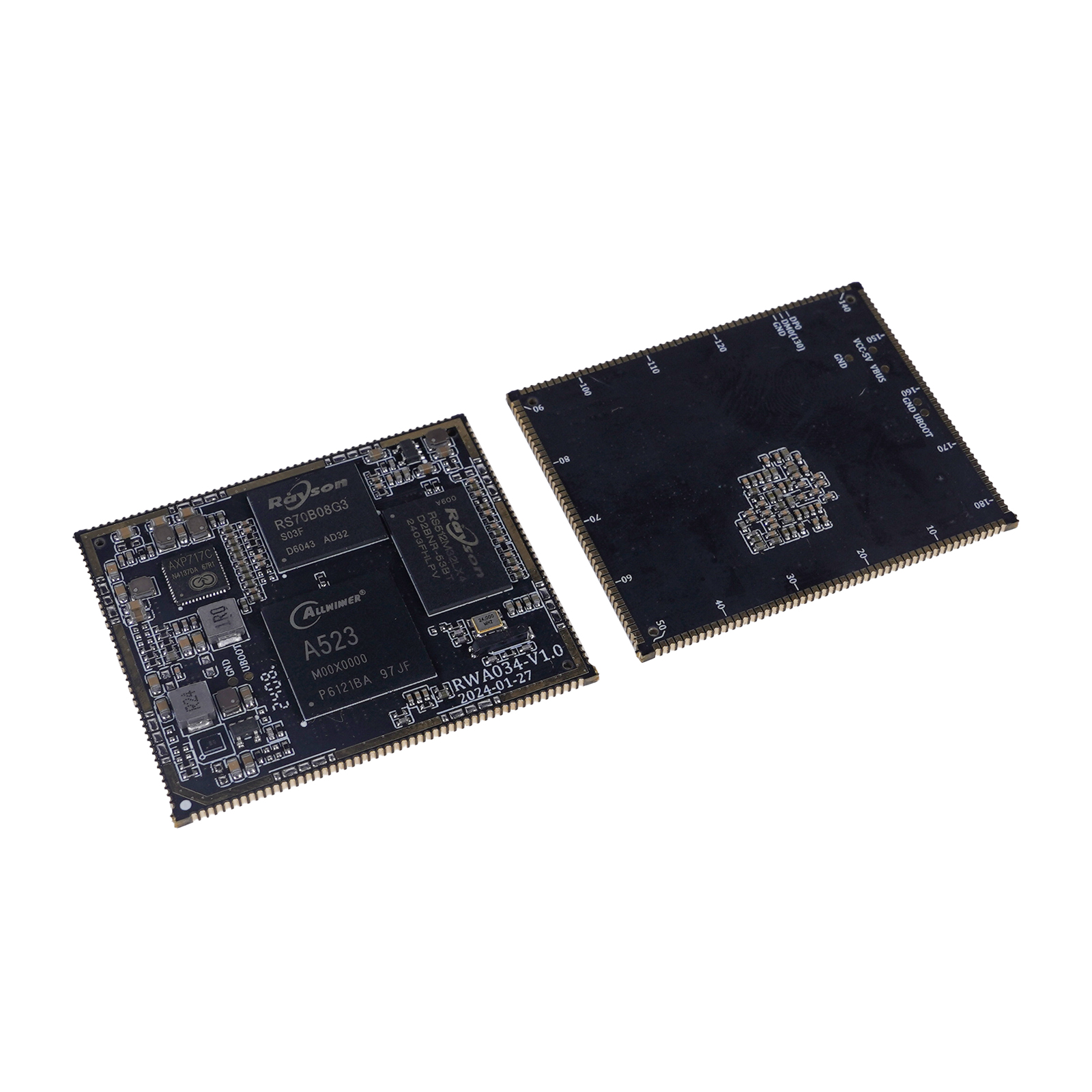

| PMU | •On board AXP717C PMU, QFN68 |

| •Support 3.9V-5.5V input, VCC-5V power input max 5V 3A |

| •Support 7xLDO from PMU,ALDO1 1.8V/3.3V 400mA; ALDO2 1.8V/3.3V 500mA; BLDO4 1.8V/3.3V 400mA; ALDO3 3.3V 200mA;CLDO4 1.8V/3.3V 500mA; CLDO1 1.8V 500mA; BLDO3 0.5V-3.5V 500mA |

| •Support 2xDCDC from SoM Board, EXT-DCDC1 powered byTCS4838, max 4.2A |

| •EXT-DCDC1 powered by SY8089A1AAC, max 1.2A |

| •Supports single cell battery |

| OS | •Defaut Android 13 OS, Linux SDK |

| •Ubuntu 18.04.6 LTS |

| •Kernel Version: 5.15 |

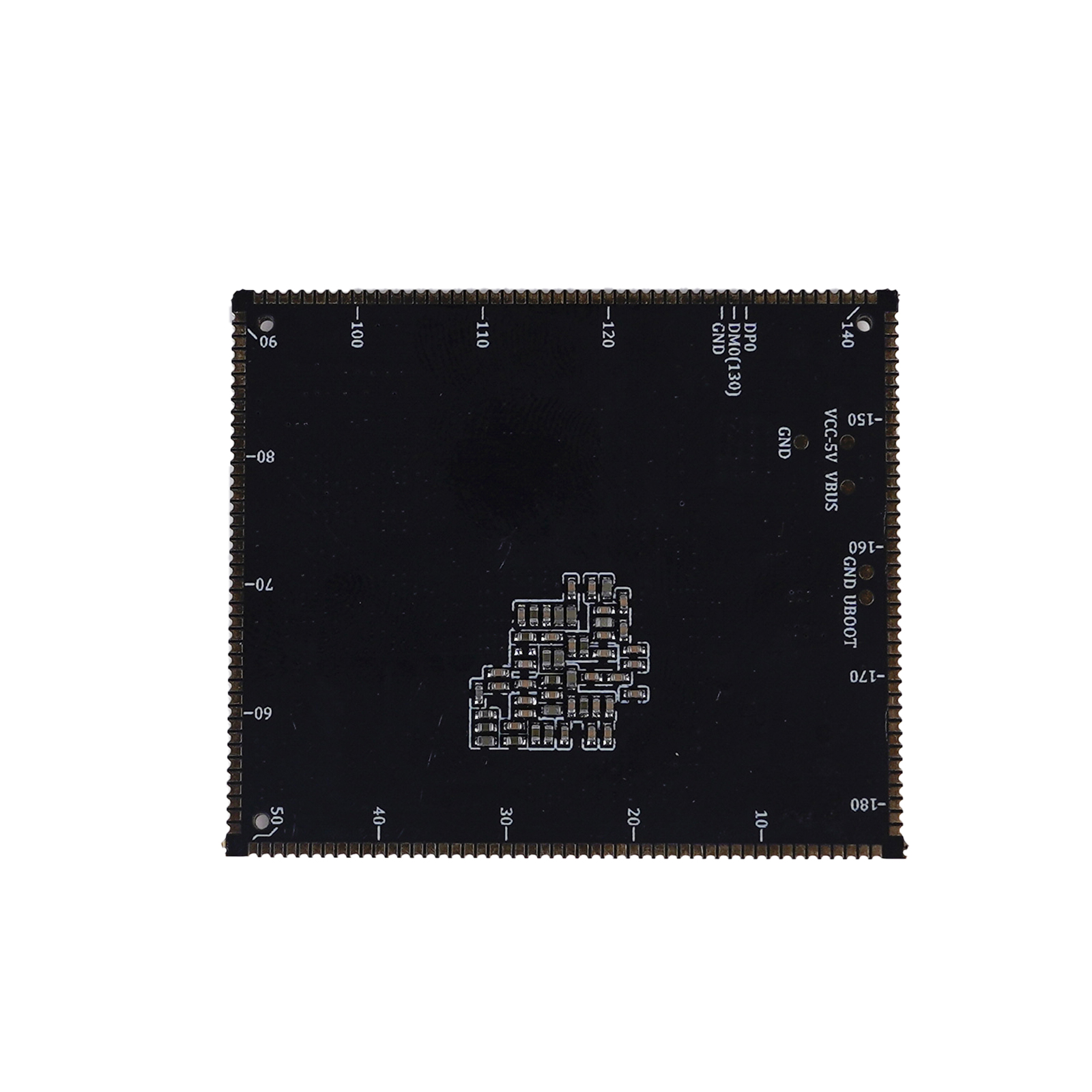

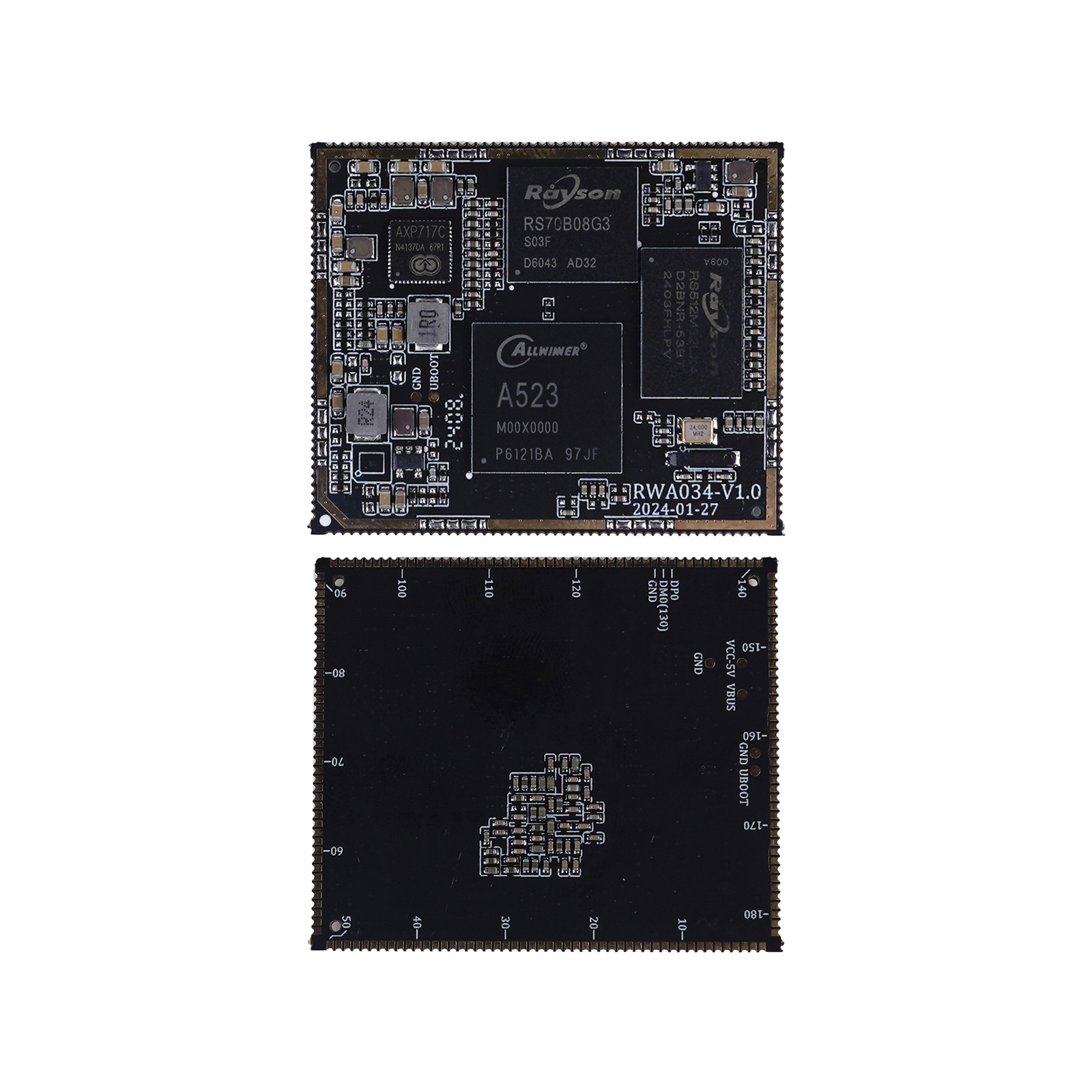

| L*W*H | 40*48*3.7mm |

Allen

Allen

Skype

Skype

Order Online

Order Online

Home

Home